# A framework for Allocation of Software Components onto a Heterogeneous Computing System

Švogor, Ivan

**Doctoral thesis / Disertacija**

2016

Degree Grantor / Ustanova koja je dodijelila akademski / stručni stupanj: University of Zagreb, Faculty of Organization and Informatics Varaždin / Sveučilište u Zagrebu, Fakultet organizacije i informatike Varaždin

Permanent link / Trajna poveznica: https://urn.nsk.hr/urn:nbn:hr:211:077581

Rights / Prava: In copyright/Zaštićeno autorskim pravom.

Download date / Datum preuzimanja: 2025-03-20

Repository / Repozitorij:

<u>Faculty of Organization and Informatics - Digital</u> Repository

#### FACULTY OF ORGANIZATION AND INFORMATICS

Ivan Švogor

# A FRAMEWORK FOR ALLOCATION OF SOFTWARE COMPONENTS ONTO A HETEROGENEOUS COMPUTING SYSTEM

**DOCTORAL THESIS**

### Sveučilište u Zagrebu

#### FAKULTET ORGANIZACIJE I INFORMATIKE

Ivan Švogor

### OKVIR ZA ALOKACIJU SOFTVERSKIH KOMPONENATA NA HETEROGENOJ RAČUNALNOJ PLATFORMI

**DOKTORSKI RAD**

Varaždin, 2016.

#### FACULTY OF ORGANIZATION AND INFORMATICS

Ivan Švogor

# A FRAMEWORK FOR ALLOCATION OF SOFTWARE COMPONENTS ONTO A HETEROGENEOUS COMPUTING SYSTEM

**DOCTORAL THESIS**

Supervisors: professor Neven Vrček professor Ivica Crnković

Varaždin, 2016

"Tis but a scratch..."

Monty Python

### **ACKNOWLEDGMENTS**

In the last few years, during the "PhD journey", I've worked with interesting people from all over the world, and since this is the Acknowledgment section it is customary to thank most memorable people along that journey. I'm keeping it as short as possible.

This journey involved a one year stay at Mälardalen University in Sweden which, except learning a great deal, turned out to be a great character building experience. The details and reasons I'll keep for myself at this point, however, people who know me best surely agree. Since this was possible only thanks to my supervisors, Ivica and Neven, I'm taking this opportunity to thank both of them, for the many hours of talking and working, lessons and patience you had with me. Thanks!

Furthermore, both in Croatia and in Sweden I got to work with good colleagues, professors and fellow PhD students with whom I spent many hours of talking, sharing delights and frustrations of being a PhD student, coding, soldering, writing research papers and a lot, a lot of coffee drinking. Thanks to everyone of you who is reading this, especially to my office mates, team mates and friends.

This thesis would never take place without the support and patience from my parents and my sister. Thanks guys! At last, thank you Antonija, for sharing this journey with me, following me at the crossroads and smoothing the bumps along the road.

Varaždin, January 2016

### **ABSTRACT**

A recent development of heterogeneous platforms (i.e. those containing different types of computing units such as multicore CPUs, GPUs, and FPGAs) has enabled significant improvements in performance of real-time data processing. However, due to increased development efforts for such platforms, they are not fully exploited. To use the full potential of such platforms, we need new frameworks and methods for capturing the optimal configuration of the software. Different configurations, i.e. allocations of software components to different computing unit types can be essential for getting the maximal utilization of the platform. For more complex systems it is difficult to find ad–hoc, good enough or the best configuration.

This research suggests the application of component based software engineering (CBSE) principles, by which it is possible to achieve the same functionality of software components across various computing units of different types, however with different extra–functional properties (EFP). The objective of this research is to construct a framework which optimizes the allocation of software components on a heterogeneous computing platform with respect to specified extra-functional requirements.

The I-IV allocation framework, proposed by this research, consist of formalisms necessary for modeling of a heterogeneous computing platform and exploring the design space, which results with an optimal design decision. The I-IV allocation framework was verified in two steps, focusing on two EFPs; the average power consumption and the average execution time. The experimental platform was a tracked robot, developed for the purpose of this research. It contains a CPU, a GPU and an FPGA, along with 32 software components deployable onto these units. Both steps resulted in a positive result confirming the claim that the I-IV framework, along with its Component allocation model  $\mathbb{M}_{\alpha}$  correctly represents the heterogeneous system performance, with consideration to multiple criteria.

### Prošireni sažetak

Usprkos tome da je u posljednjih nekoliko godina povećanje radnog takta središnje procesne jedinice (CPU) usporeno, ako ne i zaustavljeno, performanse suvremenih računala i dalje rastu, ali ne zbog radnog takta. To znači da se i performanse računalnih programa više na ovaj način ne mogu unaprijediti, čak što više, daljnje povećavanje radnog takta CPU-a pokazalo se neučinkovitim. Zbog toga, došlo je do suštinske promjene u građi procesora, odnosno to repliciranja procesnih jezgri te ugradbom dodatnih namjenskih procesnih jedinica koje su specijalizirane za određeni tip zadataka. Najčešće su to grafička procesna jedinica (GPU), programirljiva polja logičkih blokova (FPGA), integrirani krugovi specifične namjene (ASIC), itd. Istovremeno, zajednica prepoznala je veliki istraživački potencijal heterogenih računalnih sustava, odnosno sustava sa mnoštvom procesnih jedinica različitog tipa, obzirom da omogućuju izuzetna poboljšanja performansi softvera.

Mnogi se istraživači već dulje vrijeme bave heterogenim računalstvom, što znači da to nije nova ideja, no u posljednjih nekoliko godina, zbog fizičkih ograničenja vezanih uz arhitekturu procesnih jedinica, heterogeno računalstvo postaje sve popularnija istraživačka tema. Uz izuzetno povećanje procesne moći, heterogeno računalstvo donosi i mnogo izazova, prvenstveno za softverske inženjere. Naime, razvoj softvera za takve sustave vrlo je zahtjevan zbog primjerice, potrebe za rukovanjem sa više različitih tipova podataka ili programskih jezika unutar istog računalnog programa, kompatibilnosti pojedinih procesnih jedinica i konverzije tipova podataka, potrebe za specijaliziranim bibliotekama koda, korištenja različitih struktura podataka kroz više arhitekturalni slojeva računala i računalnog programa, itd. Osim toga, obzirom na to da se heterogeni sustavi prvenstveno koriste kao elementi ugradbenih računala u industriji, softverski inženjeri uz funkcionalne zahtjeve, dodatnu pozornost moraju dati ne-funkcionalnim zahtjevima (EFP).

Kako bi se upravljalo funkcionalnim i ne-funkcionalnim zahtjevima softvera, u složenim heterogenim računalnim sustavima, često se primjenjuju načela komponentno orijentiranog softverskog inženjerstva (CBSE), koja su u softverskoj zajednici dobro poznata i dokazana. CBSE obuhvaća modele, metode i smjernice za softverske inženjere koji razvijaju sustave temeljene na komponentama, odnosno građevnim jedinicama koje komuniciraju putem ugovorno definiranih sučelja, koje se mogu samostalno ugrađivati i jednostavno zamjenjivati. Time, CBSE daje snažne temelje za prethodno spomenute vezane uz razvoj softvera namijenjenog za heterogene računalne sustave. U tom kontekstu, CBSE omogućuje postizanje jednake funkcionalnosti komponenata

softvera alociranih na (različite) procesne jedinice (različitog tipa), no sa drugačijim ne-funkcionalnim svojstvima. To znači da pojedine alokacije komponenata softvera mogu biti više ili manje učinkovite obzirom na scenarije njihove primjene, odnosno njihove ulazne parametre, što za sobom povlači i pitanje ukupnih performansi sustava. Prema tome, zadatak arhitekta softvera najprije je definirati svojstva najbolje alokacije obzirom na više kriterija, poput dostupnosti resurs, ne-funkcionalna svojstva i ograničenja, a potom na konkretnoj heterogenoj računalnoj platformi učinkovito i pronaći takvu alokaciju.

Temeljni cili ovog istraživanja je konstruirati okvir za optimizaciju alokacije komponenti softvera na heterogenoj računalnoj platformi, koji uzimajući u obzir ograničenja resursa dostupnih na računalnim jedinicama (različitog tipa), specifikacije komponenata softvera i ograničenja koja definira arhitekt sustava učinkovito pronalazi najbolju alokaciju. Ova disertacija predlaže Alokacijski okvir I-IV sastavljen od formalnih elemenata koji omogućuju stvaranje modela heterogenog računalnog sustava te pretraživanje prostora potencijalnih alokacija, te definira korake kojima se postiže optimalna arhitektura sustava. Kako u ovom slučaju prostor potencijalnih rješenja, odnosno alokacija eksponencijalno raste (uz m dostupnih računalnih jedinica te n dostupnih komponenti softvera, prostor rješenja je  $m^n$ ), razvijen je i prototip alata koji automatizira Alokacijski okvir I-IV, što je inače dugotrajan ili čak neizvediv proces. Za opis ne-funkcionalnih svojstava heterogenih sustava, koristi se Model za alokaciju komponenata  $\mathbb{M}_{\alpha}$ . Taj model, primjenom težinske funkcije w omogućuje kvantifikaciju pojedinih alokacija čime je omogućena njihova usporedba te procjena prikladnosti korištenja istih. Istovremeno, težinska funkcija w daje uvid u performanse sustava u njegovoj ranoj fazi razvoja (čak prije nego su komponente razvijene).

Vjerodostojnost Alokacijskog okvira I-IV provjerena je u dva koraka (eksperimenta), pri čemu je fokus bio na dva ne-funkcionalna svojstva sustava: prosječni električni učinak električne struje i prosječno vrijeme izvođenja operacija softvera. Eksperimentalna platforma bila su robotska kolica sa heterogenim računalnim sustavom sačinjenim od CPU-a, GPU-a te FPGA-a, zajedno sa tridesetak komponenata softvera koje je moguće alocirati na te računalne jedinice.

Prvi korak provjere odnosio se na provjeru točnosti, odnosno procjenu prikladnosti težinske funkcije w da kvantificira performanse pojedine alokacije. Postupak je proveden primjenom šest različitih alokacija koje predstavljaju dva različita scenarija izvođenja. Odabrane alokacije, nakon što su kvantificirane težinskom funkcijom w, zapisane su tablično i rangirane prema predviđenim performansama. Nakon toga, te iste alokacije su implementirane na stvarnom sustavu, ranije spomenutim robotskim kolicima. Iscrpnim mjerenje (u intervalu pouzdanosti od 95%), zabilježene su performanse alokacija i ponovno su rangirane u rang listu. Rezultat oba rangiranja bio je jednak, čime slijedi da model za raspodjelu komponenata  $\mathbb{M}_{\alpha}$ , te njegova težinska funkcija w mogu korektno predvidjeti performanse pojedine alokacije u realnom sustavu. Ovakav ishod, doveo

je do drugog koraka provjere koji se odnosi na scenarij(e) u kojem postoji izrazito veliki broj komponenti softvera te računalnih jedinica, čime prostor potencijalnih rješenja postaje toliko velik pronalaženje najbolje alokacije metodom iscrpnog pretraživanja nije moguće učinkovito provesti.

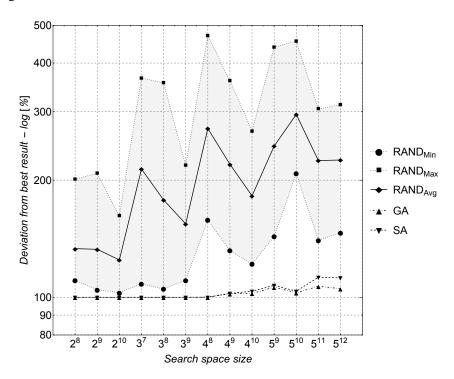

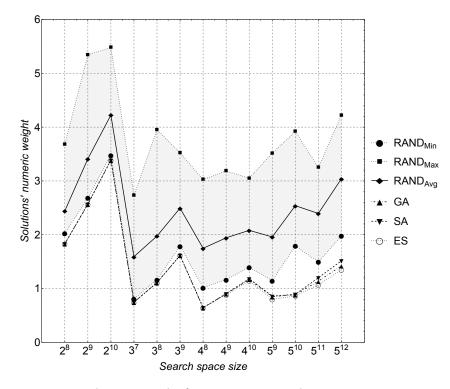

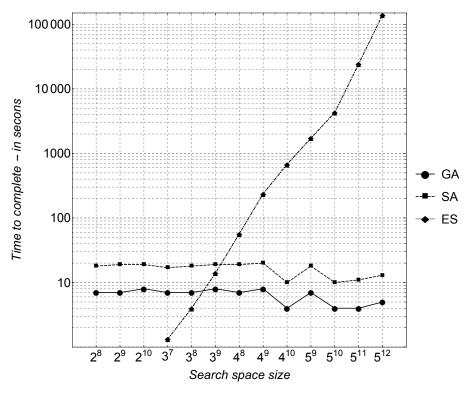

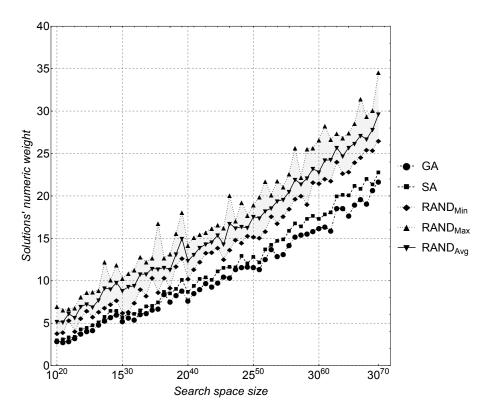

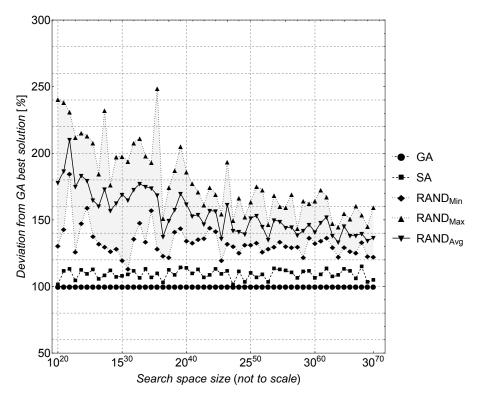

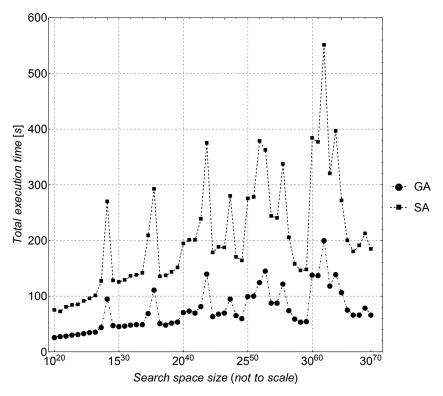

Obzirom da trenutna implementacija Alokacijskog modela I-IV definira heurističke metode za rješavanje navedenog problema, drugi korak provjere za cilj ima procijeniti sub-optimalno rješenje genetskog algoritma i metode simuliranog kaljenja. Uz heurističke metode, generirane su i proizvoljne alokacije, jer u nekim slučajevima su takve alokacije podjednako dobre ili čak bolje od heurističkih metoda. U prvoj iteraciji, provjeravala se preciznost navedenih metoda, odnosno njihovo odstupanje od optimalne alokacije dane iscrpnim pretraživanje u prostoru do  $5^{12}$ . Pokazalo se kako genetski algoritam daje najbolja rješenja, odnosno alokacije koje minimalno odstupaju od optimalnog rješenja. Nadalje, za prostore rješenja između  $10^{20}$  do  $30^{70}$  gdje iscrpno pretraživanje nije učinkovito, usporedba je pokazala da obje heurističke metode daju bolja sub-optimalne alokacije od proizvoljno definiranih alokacija i to u najkraćem vremenu. Iako je statistički vjerojatno, ni u jednom slučaju (u 55 ponavljanja, s povećavanjem prostora rješenja) nije zabilježeno da proizvoljno generirana alokacija daje bolje performanse od alokacije dobivene predloženim heurističkim metodama, čime je završila validacija predloženog okvira i svih njegovih elemenata.

### **K**EYWORDS

$heterogeneous\ computing\ platform,\ optimal\ software\ allocation,\ cyber-physical\ system,\ formal\ model,\ software\ performance\ measurement$

### **GLOSSARY**

heterogeneous

platform

a computing system which contains multiple processing units of different types (it can also be referred to as heterogeneous computing platform or heterogeneous system architecture (HSA))

heterogeneous

computing

a research discipline which deals with heterogeneous platforms

**CPU** central processing unit

**GPU** graphical processing unit

**FPGA** field programmable gate array

**ASIC** application specific integrated circuit

**CBSE** component based software engineering

**EFP** extra–functional property, a specification of a system which de-

scribes how should a system perform certain actions.

**UML** unified modeling language.

pipe-line style software architecture style in which the output of a previous

process is the input for the next process.

confidence inter-

val

a measure for expressing the uncertainty associated with a sam-

ple estimate of a population mean.

**SWEBOK** software engineering body of knowledge.

**OpenCL** open computing language library

**OpenCV** open computing vision library

**CLB** configurable logic block

**allocation** an allocation is a mapping of all n software components from

the set C to a (sub-) set of computing units U'

**I-IV framework** component allocation framework

TiWo a tracked robot, real-world platform containing a CPU, a GPU

and an FPGA.

**S,G,E,D,H** a combination of image filters executed in the given order, each

letter signifying the name of the filter. In this particular case,

Sobel, Gauss, Erode, Dilate, Hystogram.

**GA** a method for obtaining the optimal software allocation which

uses an exhaustive search.

GA a method for obtaining the (sub-) optimal software allocation

which uses a genetic algorithm.

**SA** a method for obtaining the (sub–) optimal software allocation

which uses simulated annealing

**RAND** randomly generated software allocation

# **C**ONTENTS

| 1. | Intro | oduction                                                                    | 1  |

|----|-------|-----------------------------------------------------------------------------|----|

|    | 1.1.  | Objective                                                                   | 2  |

|    | 1.2.  | Research questions                                                          | 3  |

|    | 1.3.  | Contribution                                                                | 5  |

|    | 1.4.  | Research method                                                             | 7  |

|    | 1.5.  | Thesis outline                                                              | 8  |

| 2. | Back  | rground                                                                     | 11 |

|    | 2.1.  | Software engineering                                                        | 12 |

|    |       | 2.1.1. The golden age                                                       | 12 |

|    |       | 2.1.2. Expanding body of knowledge for software engineers                   | 13 |

|    | 2.2.  | Component based software engineering                                        | 14 |

|    | 2.3.  | Hot topics in software engineering research                                 | 15 |

|    |       | 2.3.1. Software modeling for embedded systems                               | 16 |

|    |       | 2.3.2. Software architecture for embedded systems                           | 16 |

|    |       | 2.3.3. Modeling heterogeneous platforms                                     | 17 |

|    |       | 2.3.4. CPU, GPU, FPGA systems                                               | 18 |

|    |       | 2.3.5. Software component allocation                                        | 19 |

|    | 2.4.  | Heterogeneous computing                                                     | 20 |

|    |       | 2.4.1. Central processing unit                                              | 20 |

|    |       | 2.4.2. Graphical processing unit                                            | 24 |

|    |       | 2.4.3. Field programmable gate array                                        | 27 |

|    | 2.5.  | Summary                                                                     | 32 |

| 3. | Mat   | hematical model of a heterogeneous computing platform                       | 35 |

|    | 3.1.  | Introduction                                                                | 35 |

|    | 3.2.  | Allocation function                                                         | 36 |

|    | 3.3.  | The allocation cost function                                                | 38 |

|    |       | 3.3.1. Elements of the cost function                                        | 38 |

|    | 3.4.  | Constraints                                                                 | 41 |

|    |       | 3.4.1. Dismissing infeasible allocations due to limited resources           | 42 |

|    |       | 3.4.2. Dismissing infeasible allocations due to architectural specification | 44 |

|    | 3.5.  | AHP – handling different measurement units                                  | 49 |

|    |       | 3.5.1 Applying AHP to decision making in component allocation               | 40 |

| 4.1. Environment – the heterogeneous platform 4.1.1. Hardware 4.1.2. Software 4.2. The measuring procedure 4.2.1. The average execution time 4.2.2. Average power consumption measurement 4.2.3. Measurement steps and parameters 4.3. The results 4.3.1. Idle system results 4.3.2. Software component performance results – ave sumption 4.3.3. Software component performance results – ave 4.3.4. Discussion 4.4. Summary  5. I-IV Framework Verification 5.1.1. Experimental execution scenarios 5.1.2. Manually obtained allocations 5.1.3. Obtaining allocations by I-IV framework 5.1.4. SCALL – software component allocator tool 5.1.5. Experiment simulation – ranking allocations us 5.1.6. The experiment: manual allocations vs. I-IV ob 5.2. I-IV framework performance for large search spaces 5.2.1. Optimization methods 5.2.2. Optimization methods 5.2.3. Summary  6. Related work 6.1. Research classification 6.2. Software architecture physical footprint 7. Conclusion 7.1. Model of the heterogeneous platform 7.2. Measurement of software allocation performance                                                                                                                                                                                                                                                                                                       |     | 3.6. | Accoun                    | nting for the <i>synergy effect</i>                                     | 54  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|---------------------------|-------------------------------------------------------------------------|-----|

| <ul> <li>4.1. Environment – the heterogeneous platform 4.1.1. Hardware 4.1.2. Software</li> <li>4.2. The measuring procedure 4.2.1. The average execution time 4.2.2. Average power consumption measurement 4.2.3. Measurement steps and parameters 4.3. The results 4.3.1. Idle system results 4.3.2. Software component performance results – ave sumption 4.3.3. Software component performance results – ave 4.3.4. Discussion 4.4. Summary  5. I-IV Framework Verification 5.1.</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     | 3.7. | Summ                      | ary                                                                     | 57  |

| <ul> <li>4.1.1. Hardware</li> <li>4.1.2. Software</li> <li>4.2. The measuring procedure</li> <li>4.2.1. The average execution time</li> <li>4.2.2. Average power consumption measurement</li> <li>4.2.3. Measurement steps and parameters</li> <li>4.3. The results</li> <li>4.3.1. Idle system results</li> <li>4.3.2. Software component performance results – ave sumption</li> <li>4.3.3. Software component performance results – ave</li> <li>4.3.4. Discussion</li> <li>4.4. Summary</li> <li>5. I-IV Framework Verification</li> <li>5.1.1. Experimental execution scenarios</li> <li>5.1.2. Manually obtained allocations</li> <li>5.1.3. Obtaining allocations by <i>I-IV</i> framework</li> <li>5.1.4. SCALL – software component allocator tool</li> <li>5.1.5. Experiment simulation – ranking allocations us</li> <li>5.1.6. The experiment: manual allocations vs. I-IV ob</li> <li>5.2. I-IV framework performance for large search spaces</li> <li>5.2.1. Optimization methods</li> <li>5.2.2. Optimizing the software architecture</li> <li>5.3. Summary</li> <li>6. Related work</li> <li>6.1. Research classification</li> <li>6.2. Software architecture optimization</li> <li>6.3. Software architecture physical footprint</li> <li>7. Conclusion</li> <li>7.1. Model of the heterogeneous platform</li> <li>7.2. Measurement of software allocation performance</li> </ul> | 4.  | Mea  | sureme                    | ent                                                                     | 59  |

| <ul> <li>4.1.2. Software</li> <li>4.2. The measuring procedure <ul> <li>4.2.1. The average execution time</li> <li>4.2.2. Average power consumption measurement</li> <li>4.2.3. Measurement steps and parameters</li> </ul> </li> <li>4.3. The results <ul> <li>4.3.1. Idle system results</li> <li>4.3.2. Software component performance results – ave sumption</li> <li>4.3.3. Software component performance results – ave 4.3.4. Discussion</li> <li>4.4. Summary</li> </ul> </li> <li>5. I-IV Framework Verification <ul> <li>5.1.1. Experimental execution scenarios</li> <li>5.1.2. Manually obtained allocations</li> <li>5.1.3. Obtaining allocations by I-IV framework</li> <li>5.1.4. SCALL – software component allocator tool</li> <li>5.1.5. Experiment simulation – ranking allocations us</li> <li>5.1.6. The experiment: manual allocations vs. I-IV ob</li> </ul> </li> <li>5.2. I-IV framework performance for large search spaces</li> <li>5.2.1. Optimization methods</li> <li>5.2.2. Optimizing the software architecture</li> <li>5.3. Summary</li> <li>6. Related work</li> <li>6.1. Research classification</li> <li>6.2. Software architecture optimization</li> <li>6.3. Software architecture physical footprint</li> </ul> <li>7. Conclusion</li> <li>7.1. Model of the heterogeneous platform</li> <li>7.2. Measurement of software allocation performance</li>      |     | 4.1. | Enviro                    | nment – the heterogeneous platform                                      | 59  |

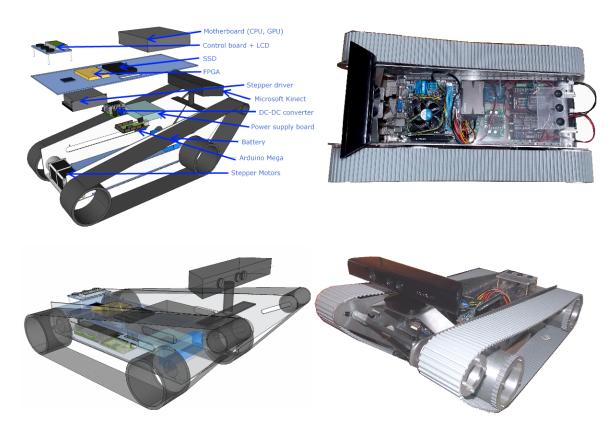

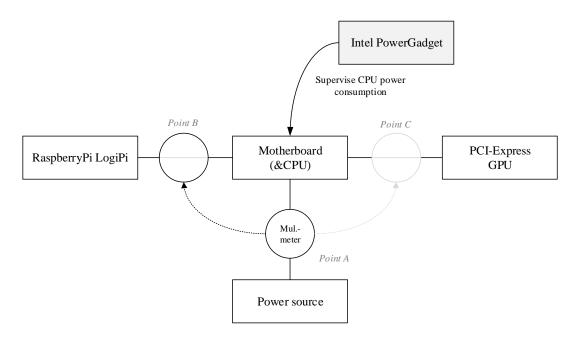

| <ul> <li>4.2. The measuring procedure 4.2.1. The average execution time 4.2.2. Average power consumption measurement 4.2.3. Measurement steps and parameters 4.3. The results 4.3.1. Idle system results 4.3.2. Software component performance results – ave sumption 4.3.3. Software component performance results – ave 4.3.4. Discussion 4.4. Summary  5. I-IV Framework Verification 5.1.1. Experimental execution scenarios 5.1.2. Manually obtained allocations 5.1.3. Obtaining allocations by <i>I-IV</i> framework 5.1.4. SCALL – software component allocator tool 5.1.5. Experiment simulation – ranking allocations us 5.1.6. The experiment: manual allocations vs. I-IV ob 5.2. I-IV framework performance for large search spaces 5.2.1. Optimization methods 5.2.2. Optimizing the software architecture 5.3. Summary  6. Related work 6.1. Research classification 6.2. Software architecture optimization 6.3. Software architecture physical footprint 7. Conclusion 7.1. Model of the heterogeneous platform 7.2. Measurement of software allocation performance</li> </ul>                                                                                                                                                                                                                                                                                                    |     |      | 4.1.1.                    | Hardware                                                                | 60  |

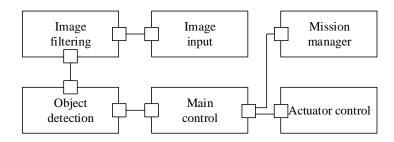

| <ul> <li>4.2.1. The average execution time 4.2.2. Average power consumption measurement . 4.2.3. Measurement steps and parameters . 4.3.1. Idle system results 4.3.2. Software component performance results – ave sumption 4.3.3. Software component performance results – ave 4.3.4. Discussion . 4.4. Summary . 5. I-IV Framework Verification 5.1.1. Experimental execution scenarios . 5.1.2. Manually obtained allocations . 5.1.3. Obtaining allocations by I-IV framework . 5.1.4. SCALL – software component allocator tool . 5.1.5. Experiment simulation – ranking allocations us 5.1.6. The experiment: manual allocations vs. I-IV ob 5.2. I-IV framework performance for large search spaces . 5.2.1. Optimization methods . 5.2.2. Optimizing the software architecture . 5.3. Summary . 6. Related work 6.1. Research classification . 6.2. Software architecture optimization . 6.3. Software architecture physical footprint . 7. Conclusion 7.1. Model of the heterogeneous platform . 7.2. Measurement of software allocation performance .</li> </ul>                                                                                                                                                                                                                                                                                                                         |     |      | 4.1.2.                    | Software                                                                | 62  |

| <ul> <li>4.2.2. Average power consumption measurement .</li> <li>4.2.3. Measurement steps and parameters</li> <li>4.3.1. Idle system results</li> <li>4.3.2. Software component performance results – ave sumption</li> <li>4.3.3. Software component performance results – ave 4.3.4. Discussion</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     | 4.2. | The m                     | easuring procedure                                                      | 65  |

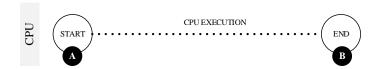

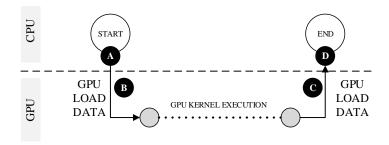

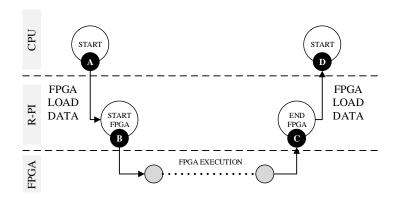

| <ul> <li>4.2.3. Measurement steps and parameters</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |      | 4.2.1.                    | The average execution time                                              | 65  |

| <ul> <li>4.3. The results 4.3.1. Idle system results 4.3.2. Software component performance results – ave sumption 4.3.3. Software component performance results – ave 4.3.4. Discussion 4.4. Summary 5. I-IV Framework Verification 5.1.1. Experimental execution scenarios 5.1.2. Manually obtained allocations 5.1.3. Obtaining allocations by <i>I-IV</i> framework 5.1.4. SCALL – software component allocator tool 5.1.5. Experiment simulation – ranking allocations us 5.1.6. The experiment: manual allocations vs. I-IV ob 5.2. I-IV framework performance for large search spaces 5.2.1. Optimization methods 5.2.2. Optimizing the software architecture 5.3. Summary 6. Related work 6.1. Research classification 6.2. Software architecture optimization 6.3. Software architecture physical footprint 7. Conclusion 7.1. Model of the heterogeneous platform 7.2. Measurement of software allocation performance</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |      | 4.2.2.                    | Average power consumption measurement                                   | 67  |

| <ul> <li>4.3.1. Idle system results</li> <li>4.3.2. Software component performance results – av sumption</li> <li>4.3.3. Software component performance results – ave 4.3.4. Discussion</li> <li>4.4. Summary</li> <li>5. I-IV Framework Verification</li> <li>5.1.1. Experimental execution scenarios</li> <li>5.1.2. Manually obtained allocations</li> <li>5.1.3. Obtaining allocations by <i>I-IV</i> framework</li> <li>5.1.4. SCALL – software component allocator tool</li> <li>5.1.5. Experiment simulation – ranking allocations us</li> <li>5.1.6. The experiment: manual allocations vs. I-IV ob</li> <li>5.2. I-IV framework performance for large search spaces</li> <li>5.2.1. Optimization methods</li> <li>5.2.2. Optimizing the software architecture</li> <li>5.3. Summary</li> <li>6. Related work</li> <li>6.1. Research classification</li> <li>6.2. Software architecture optimization</li> <li>6.3. Software architecture physical footprint</li> <li>7. Conclusion</li> <li>7.1. Model of the heterogeneous platform</li> <li>7.2. Measurement of software allocation performance</li> </ul>                                                                                                                                                                                                                                                                               |     |      | 4.2.3.                    | Measurement steps and parameters                                        | 70  |

| <ul> <li>4.3.2. Software component performance results – ave sumption</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     | 4.3. | The re                    | sults                                                                   | 78  |

| sumption                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |      | 4.3.1.                    | Idle system results                                                     | 79  |

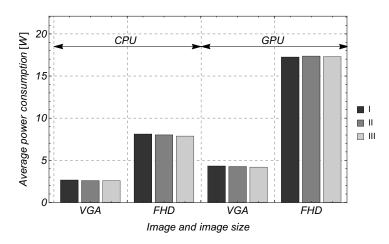

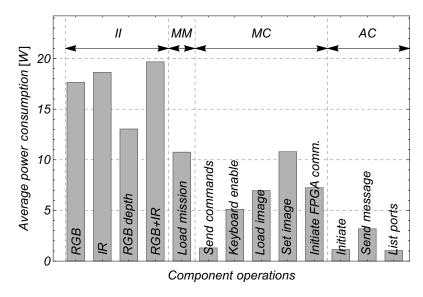

| <ul> <li>4.3.3. Software component performance results – ave 4.3.4. Discussion</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |      | 4.3.2.                    | Software component performance results – average power con-             |     |

| $4.3.4. \   \text{Discussion}  .  .  .  .  .  .  .  .  .  $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |      |                           | sumption                                                                | 81  |

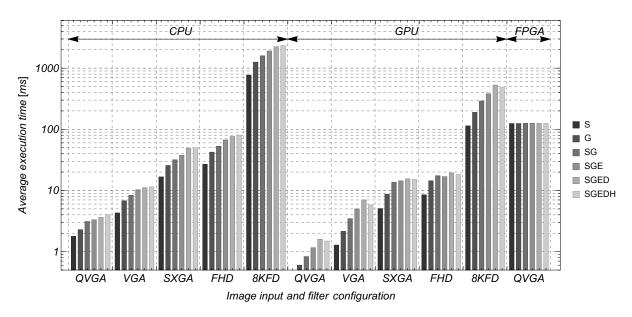

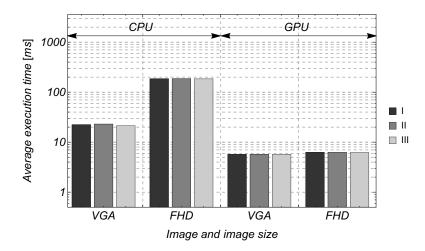

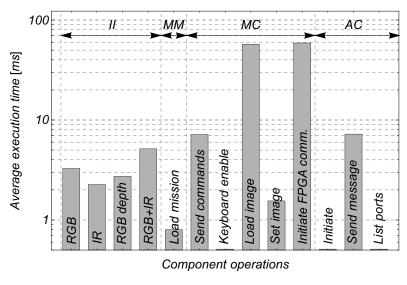

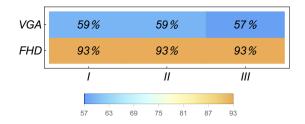

| <ul> <li>4.4. Summary</li> <li>5. I-IV Framework Verification</li> <li>5.1.1. Experimental execution scenarios</li> <li>5.1.2. Manually obtained allocations</li> <li>5.1.3. Obtaining allocations by <i>I-IV</i> framework</li> <li>5.1.4. SCALL – software component allocator tool</li> <li>5.1.5. Experiment simulation – ranking allocations us</li> <li>5.1.6. The experiment: manual allocations vs. I-IV ob</li> <li>5.2. I-IV framework performance for large search spaces</li> <li>5.2.1. Optimization methods</li> <li>5.2.2. Optimizing the software architecture</li> <li>5.3. Summary</li> <li>6. Related work</li> <li>6.1. Research classification</li> <li>6.2. Software architecture optimization</li> <li>6.3. Software architecture physical footprint</li> <li>7. Conclusion</li> <li>7.1. Model of the heterogeneous platform</li> <li>7.2. Measurement of software allocation performance</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |      | 4.3.3.                    | Software component performance results – average execution time         | 85  |

| <ul> <li>5. I-IV Framework Verification</li> <li>5.1. M<sub>α</sub> validation</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |      | 4.3.4.                    | Discussion                                                              | 89  |

| <ul> <li>5.1. M<sub>α</sub> validation</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     | 4.4. | Summ                      | ary                                                                     | 91  |

| 5.1.1. Experimental execution scenarios                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 5.  | I-IV | Framev                    | work Verification                                                       | 93  |

| 5.1.2. Manually obtained allocations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     | 5.1. | $\mathbb{M}_{\alpha}$ val | lidation                                                                | 93  |

| 5.1.3. Obtaining allocations by <i>I-IV</i> framework 5.1.4. SCALL – software component allocator tool . 5.1.5. Experiment simulation – ranking allocations us 5.1.6. The experiment: manual allocations vs. I-IV ob 5.2. I-IV framework performance for large search spaces . 5.2.1. Optimization methods                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |      | 5.1.1.                    | Experimental execution scenarios                                        | 94  |

| 5.1.3. Obtaining allocations by <i>I-IV</i> framework 5.1.4. SCALL – software component allocator tool . 5.1.5. Experiment simulation – ranking allocations us 5.1.6. The experiment: manual allocations vs. I-IV ob 5.2. I-IV framework performance for large search spaces . 5.2.1. Optimization methods                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |      | 5.1.2.                    | Manually obtained allocations                                           | 96  |

| 5.1.5. Experiment simulation – ranking allocations us 5.1.6. The experiment: manual allocations vs. I-IV ob 5.2. I-IV framework performance for large search spaces . 5.2.1. Optimization methods                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |      |                           | Obtaining allocations by <i>I-IV</i> framework                          | 97  |

| 5.1.6. The experiment: manual allocations vs. I-IV ob 5.2. I-IV framework performance for large search spaces . 5.2.1. Optimization methods                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |      | 5.1.4.                    | SCALL – software component allocator tool                               | 102 |

| 5.2. I-IV framework performance for large search spaces . 5.2.1. Optimization methods                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |      | 5.1.5.                    | Experiment simulation – ranking allocations using $\mathbb{M}_{\alpha}$ | 105 |

| 5.2.1. Optimization methods                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |      | 5.1.6.                    | The experiment: manual allocations vs. I-IV obtained allocations        | 107 |

| 5.2.2. Optimizing the software architecture 5.3. Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     | 5.2. | I-IV fra                  | amework performance for large search spaces                             | 109 |

| <ul> <li>5.3. Summary</li> <li>6. Related work</li> <li>6.1. Research classification</li> <li>6.2. Software architecture optimization</li> <li>6.3. Software architecture physical footprint</li> <li>7. Conclusion</li> <li>7.1. Model of the heterogeneous platform</li> <li>7.2. Measurement of software allocation performance</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |      | 5.2.1.                    | Optimization methods                                                    | 109 |

| <ul> <li>6. Related work</li> <li>6.1. Research classification</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |      | 5.2.2.                    | Optimizing the software architecture                                    | 112 |

| <ul> <li>6.1. Research classification</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     | 5.3. | Summ                      | ary                                                                     | 121 |

| <ul> <li>6.1. Research classification</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 6.  | Rela | ted wo                    | rk                                                                      | 125 |

| <ul> <li>6.2. Software architecture optimization</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |      |                           |                                                                         | 125 |

| <ul> <li>6.3. Software architecture physical footprint</li> <li>7. Conclusion</li> <li>7.1. Model of the heterogeneous platform</li> <li>7.2. Measurement of software allocation performance</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |      |                           |                                                                         | 126 |

| <ul><li>7.1. Model of the heterogeneous platform</li><li>7.2. Measurement of software allocation performance</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |      |                           |                                                                         | 129 |

| <ul><li>7.1. Model of the heterogeneous platform</li><li>7.2. Measurement of software allocation performance</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 7   | Cone | clusion                   |                                                                         | 131 |

| 7.2. Measurement of software allocation performance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | , • |      |                           |                                                                         | 131 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |      |                           |                                                                         | 132 |

| 7.5. I-IV Halliework acceptability.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |      |                           |                                                                         | 132 |

| 7.4. | Research questions and research goals | 134 |

|------|---------------------------------------|-----|

| 7.5. | Future work                           | 136 |

# LIST OF FIGURES

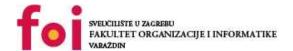

| 1.1. | Three-phase research method developed and used in this thesis                                                                                                                                                                                                      | 8  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

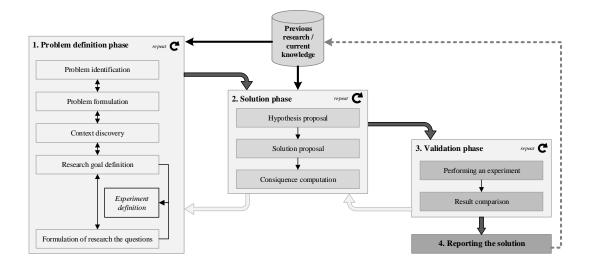

| 2.1. | CPU Architecture, left image shows a hierarchical design multicore processor where cores share L3, and have their own L1 and L2 (AMD), while the right figure shows a design where two cores share L2, and communicate via a memory controller (Intel) (from [90]) | 23 |

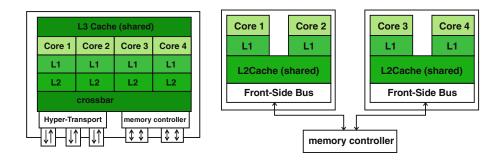

| 2.2. | GPU Architecture of nVidia GeForce 8800 (from [90]). SP is a streaming                                                                                                                                                                                             | ۷3 |

|      | processor, TF is a texture filtering unit, TA is a texture address unit                                                                                                                                                                                            | 25 |

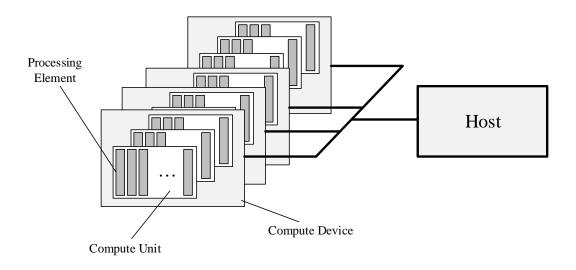

| 2.3. | OpenCL platform model                                                                                                                                                                                                                                              | 26 |

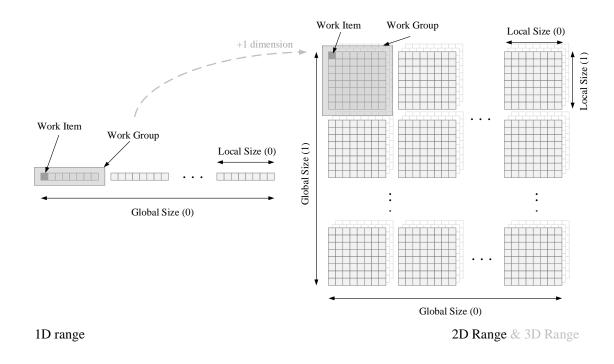

| 2.4. | OpenCL Data–Parallelism, left side of the image shows data-parallelism operationg over an array, while the right part shows data-parallelism for                                                                                                                   |    |

|      | an image                                                                                                                                                                                                                                                           | 27 |

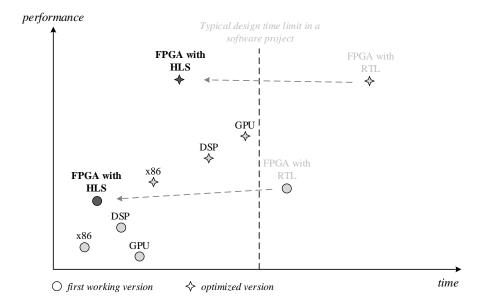

| 2.5. | Design time vs. application performance (from [122]). A design shift from register–transfel level (RTL) model to hardware–level synthesis (HLS)                                                                                                                    |    |

|      | dramatically reduced the design time while keeping the application per-                                                                                                                                                                                            | 00 |

| 0.6  | formance                                                                                                                                                                                                                                                           | 29 |

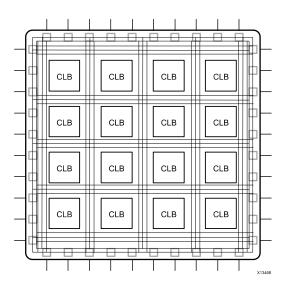

|      | FPGA Architecture (from [122])                                                                                                                                                                                                                                     | 30 |

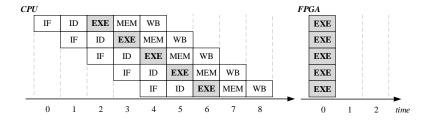

|      | Instruction execution, CPU vs FPGA (from [122])                                                                                                                                                                                                                    | 30 |

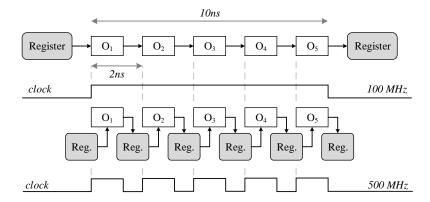

| 2.8. | FPGA pipelining, depending on usage scenarios, a FPGA developer can                                                                                                                                                                                                |    |

|      | choose different implementation options, where as for a CPU or a GPU                                                                                                                                                                                               | 01 |

|      | the design is permanent                                                                                                                                                                                                                                            | 31 |

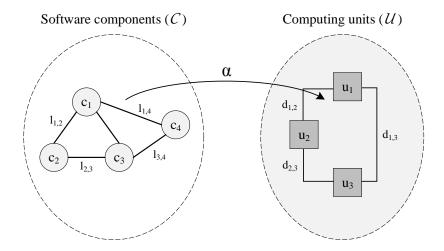

| 3.1. | Mapping, i.e. allocating software components to computing units                                                                                                                                                                                                    | 37 |

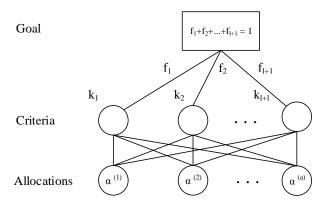

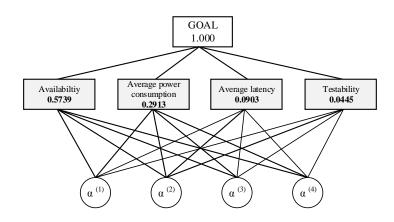

| 3.2. | Hierarchy for defining the criteria                                                                                                                                                                                                                                | 50 |

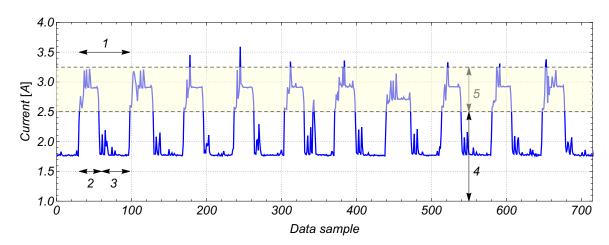

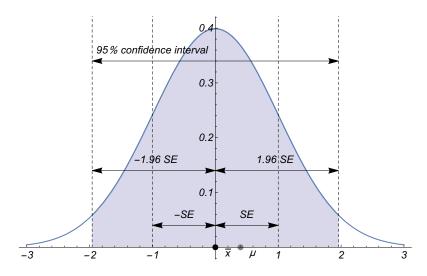

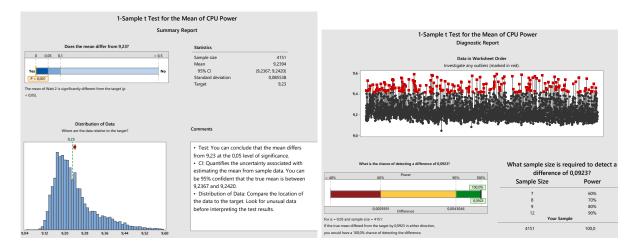

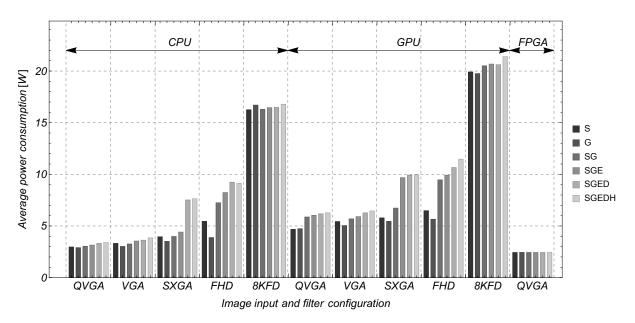

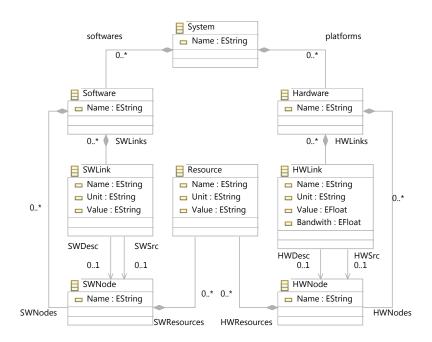

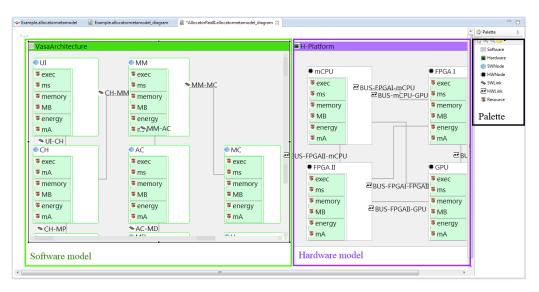

| 3.3. | AHP hierarchy example with four criteria and four alternatives                                                                                                                                                                                                     | 52 |